## Lecture 14

## Timing Constraints & Timing Analysis

Peter Cheung Imperial College London

URL: www.ee.imperial.ac.uk/pcheung/teaching/E2\_CAS/ E-mail: p.cheung@imperial.ac.uk

### **Lecture Objectives**

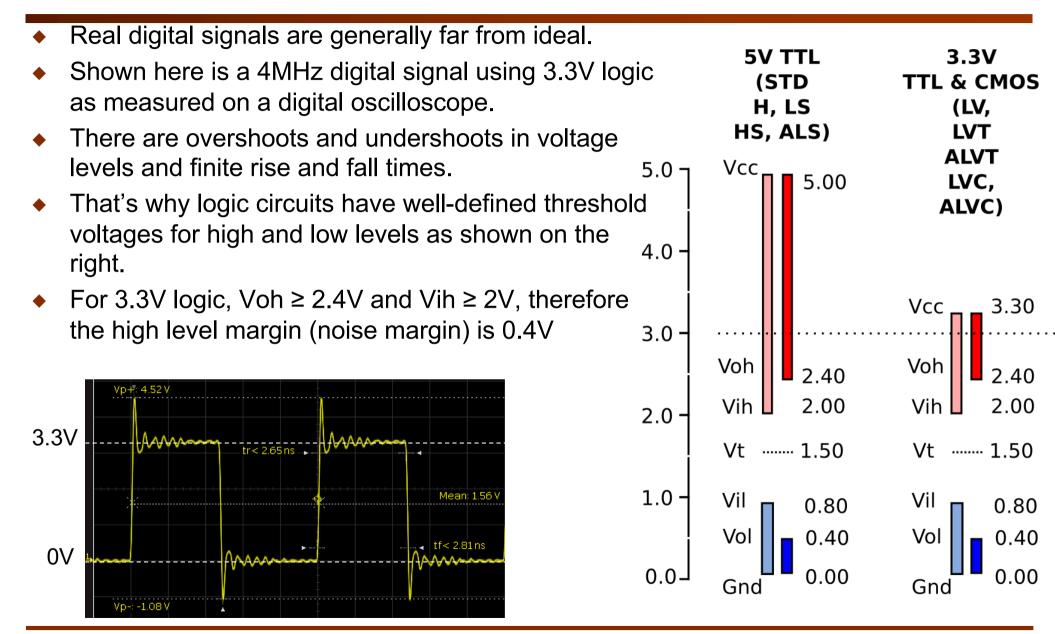

- Appreciate the difference between theoretical and real digital signals

- Understand the low and high logic level thresholds for input and output digital signals

- Understand the meaning of noise margin and why they are needed

- Explain the meaning of setup and hold times in flipflops

- Explain how data is sent between two digital systems using a synchronous bitserial protocol

- Investigate the timing constraints in a transmission system

- Explore the **TimeQuest** timing analyser used in the Quartus system

## **Typical digital signal**

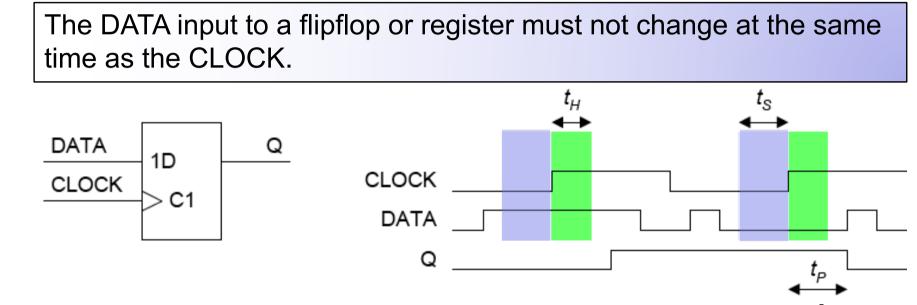

### **Setup and Hold Times**

**Setup Time**: DATA must reach its new value at least  $t_s$  before the CLOCK<sup>↑</sup> edge.

**Hold Time**: DATA must be held constant for at least  $t_H$  after the CLOCK<sup>↑</sup> edge.

- Typical values for a register:  $t_S = 5$  ns,  $t_H = 3$  ns (discrete logic/ I/O circuit)  $t_S = -50$ ps,  $t_H = 0.2$  ns (internal LE)

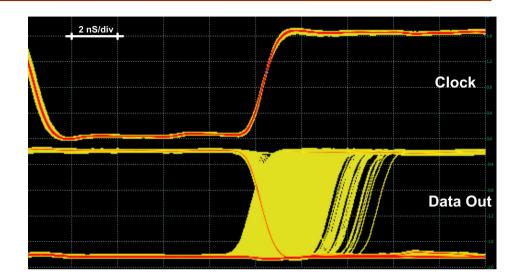

- If these requirements are not met, the Q output may oscillate for many nanoseconds before settling to a stable value.

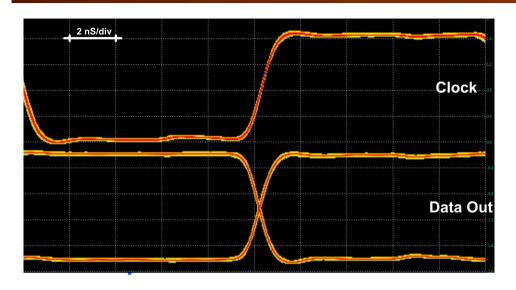

#### Setup time violation and metastability

- No setup time violation

- Input data arrives earlier than t<sub>s</sub> before rising edge of Clock

- Data Out changes cleanly to either 0 or 1

- Set up time violation

- Input data arrives within the setup time window t<sub>s</sub>

- Data Out becomes undefined (0 or 1 or somewhere in between) for a random period time before settling down to either 0 or 1

- This can cause the digital circuit to fail

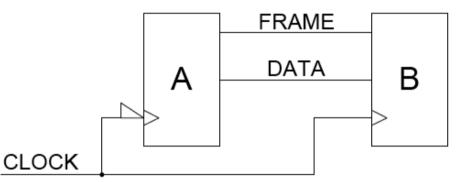

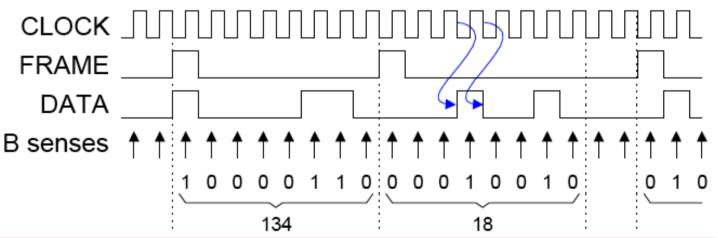

## **Synchronous Bit-Serial Transmission**

Transmitting 8 bit values from A to B:

- FRAME indicates the first bit of each value; the other 7 bits follow on consecutive clock cycles. The FRAME signal is often called a frame sync pulse.

- DATA changes on the *falling* CLOCK edge

- Propagation delays are often omitted from diagram.

- DATA is sensed by system B on the <u>rising</u> CLOCK edge to maximise tolerance to timing errors. We must always clock a flipflop at a time when its DATA input is not changing.

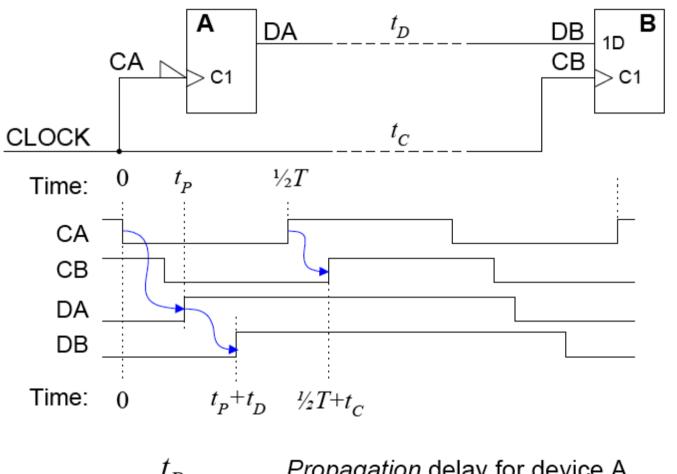

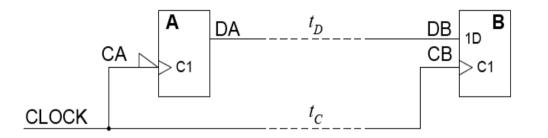

## **Timing Specifications**

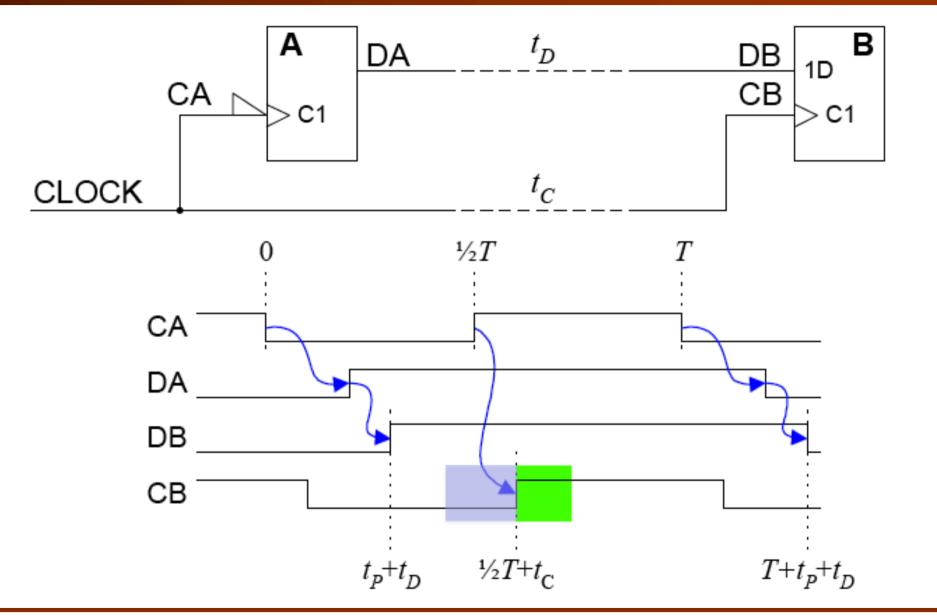

#### For Device B:

Data input changes at time  $t_P + t_D$

◆Clock input changes ↑ at time  $\frac{1}{2}T+t_C$

- $t_P$ Propagation delay for device A. Т

- Clock Period.

- $t_C, t_D$ Transmission line delays for CLOCK and DATA

### **Timing Constraints (1)**

# **Timing Constraints (2)**

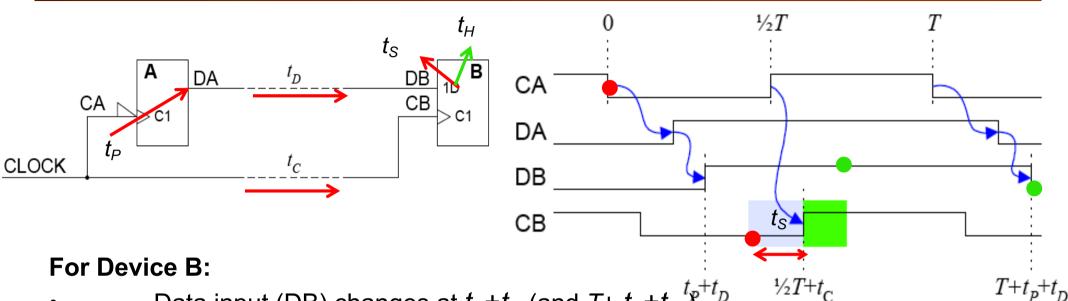

- Data input (DB) changes at  $t_P + t_D$  (and  $T + t_P + t_D^{t_P + t_D}$ )

- Clock<sup>↑</sup> (CB) at time  $\frac{1}{2}T+t_C$

#### For reliable operation:

- Setup Requirement:  $t_P + t_D + t_S < \frac{1}{2}T + t_C$

- Hold Requirement:  $\frac{1}{2}T + t_C + t_H < T + t_P + t_D$

Get a pair of inequalities for each flipflop/register in a circuit. You never get both  $t_S$  and  $t_H$  in the same inequality.

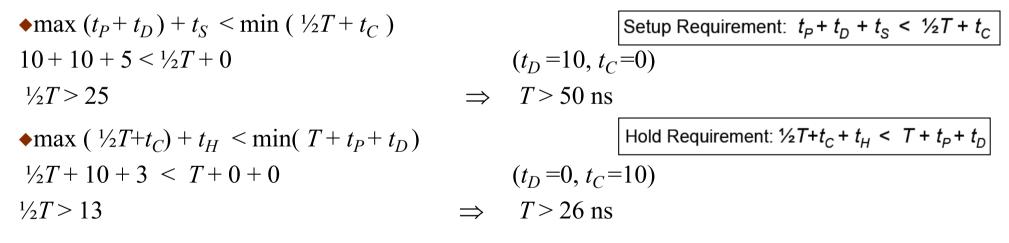

#### Example

For a given DSP processor:  $0 < t_P < 10 \text{ ns}, t_S = 5 \text{ ns}, t_H = 3 \text{ ns}$ Suppose differential delay:  $-10 < (t_D - t_C) < +10$

Find maximum CLOCK frequency (min CLOCK period):

```

•Hence f_{CLOCK} < 1/50ns = 20 MHz

```

•To test for worst case: make the left side of the inequality as big as possible and the right side as small as possible.

### **Propagation Delay Constraint Inequalities**

#### When do they arise?

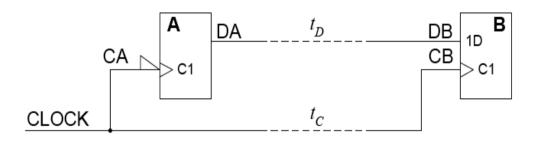

Whenever a flipflop's clock and data input signals originate from the same ultimate source. Here CB and DB both originate from CLOCK. You normally get two inequalities for each flipflop in a circuit.

#### Relationship between setup and hold inequalities:

- Setup Requirement:  $t_P + t_D + t_S < \frac{1}{2}T + t_C$

- Hold Requirement:  $\frac{1}{2}T+t_{C}+t_{H} < t_{P}+t_{D}+T$

#### Are both $t_s$ and $t_H$ ever in the same inequality?

• No.

#### How do you decide to take the max or the min?

- For a <, take max of everything on the left and min of everything on the right.

- max = most positive: for example, max(-7,-2) = -2

IMPORTANT: These inequalities applies ONLY to this circuit. IT IS NOT UNIVERSAL!

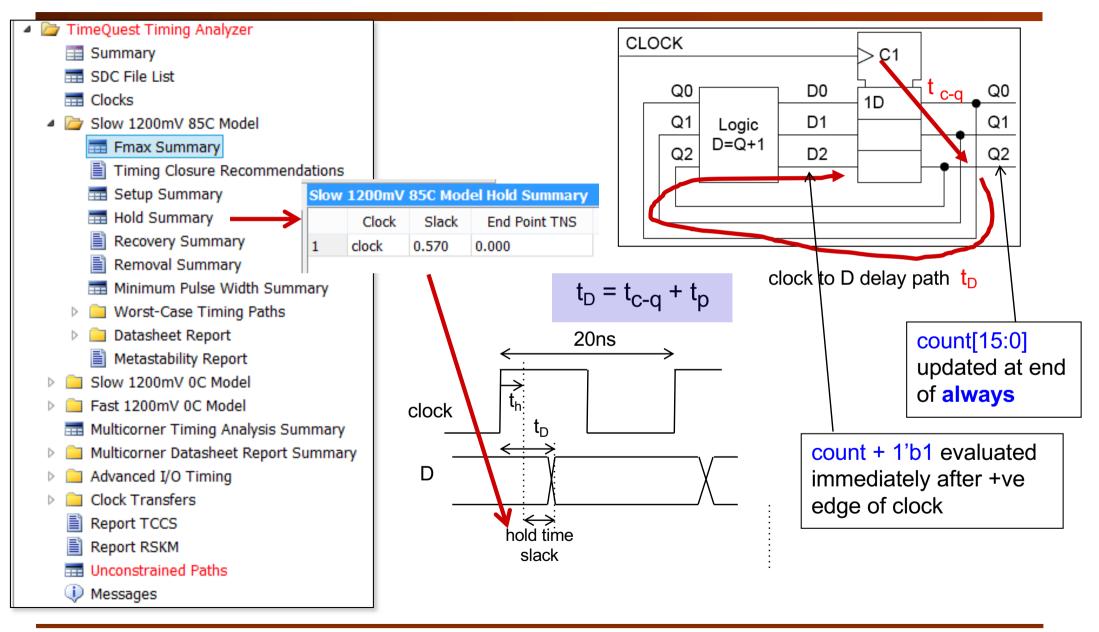

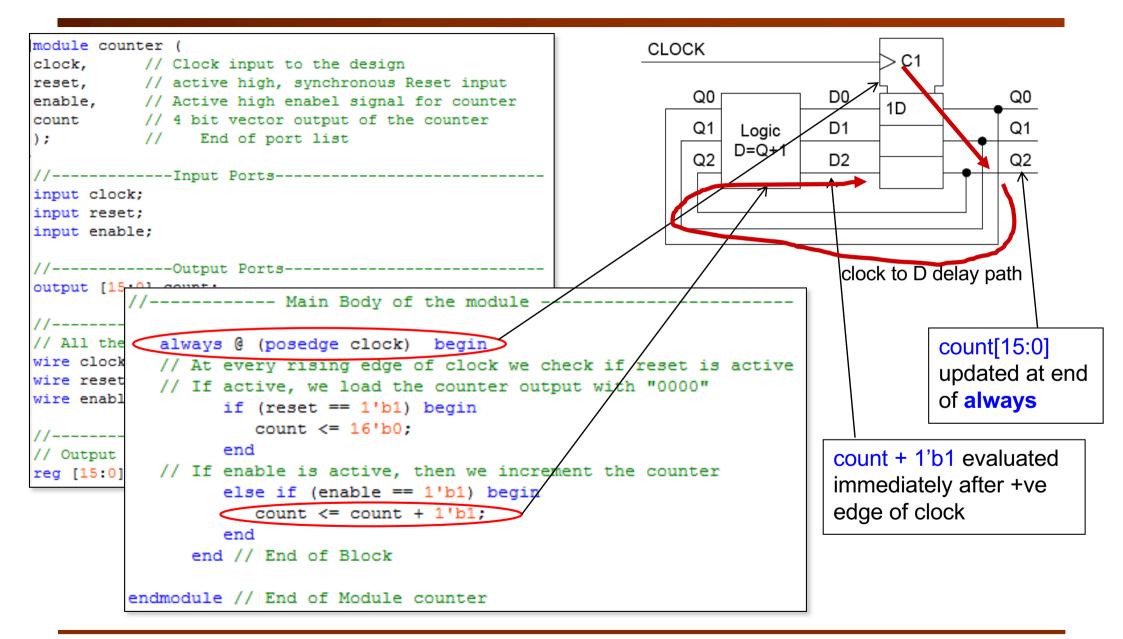

#### The 16-bit up-counter

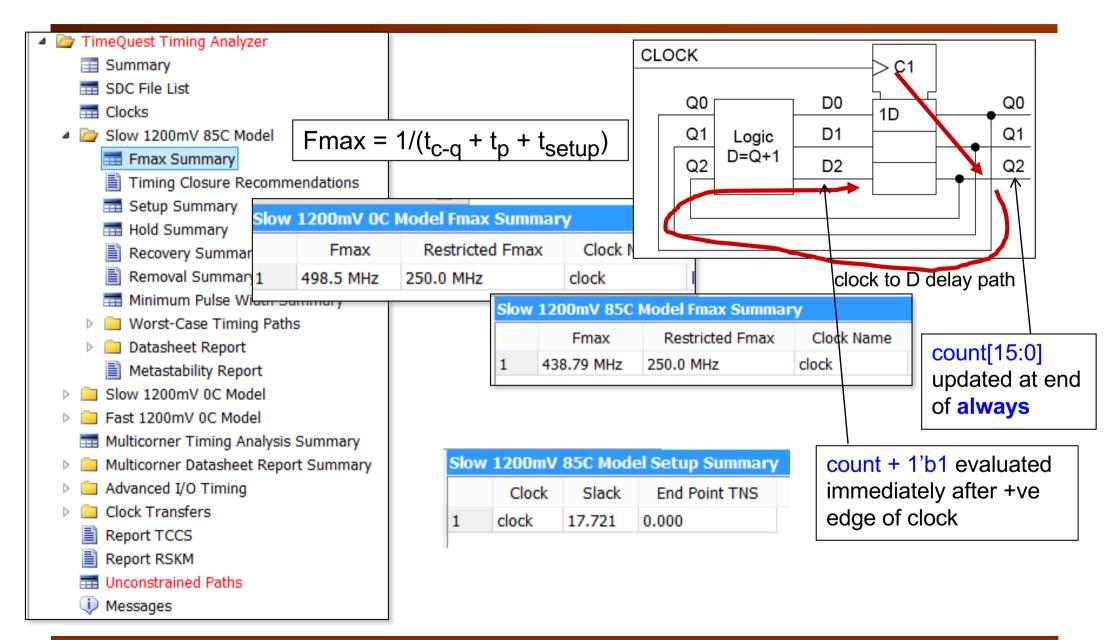

## **TimeQuest Report (1) - Fmax**

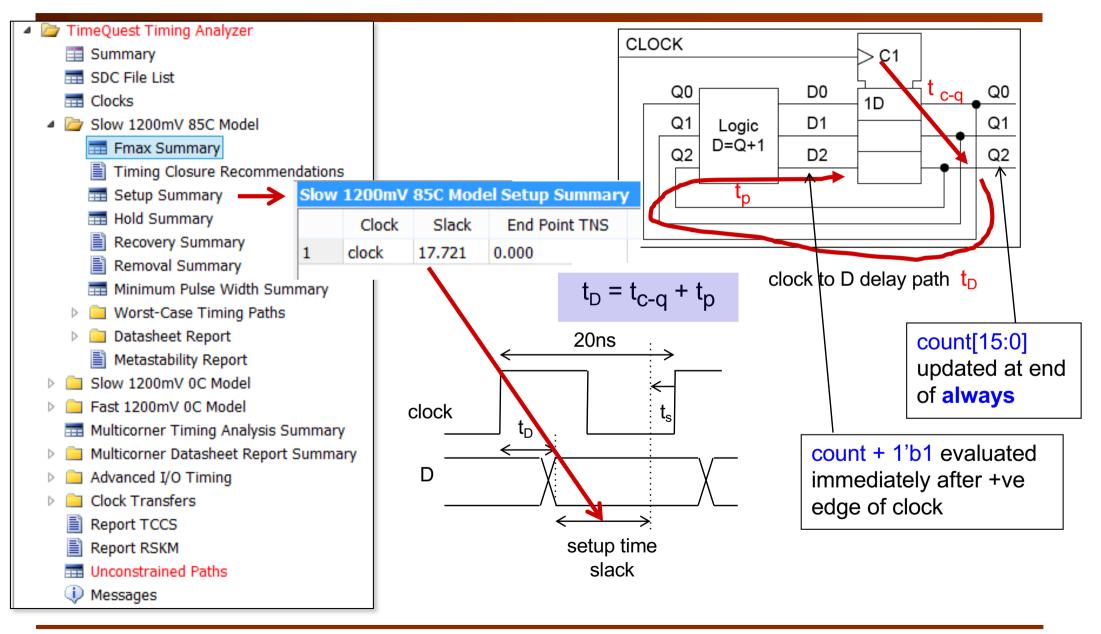

## **TimeQuest Report (2) – Setup Summary**

### **TimeQuest Report (2) – Hold Summary**